### HY5117404B Series 4M x 4-bit CMOS DRAM with Extended Data Out

PRELIMINARY

28 DVSS 25 DQ 24 DNC 23 DCAS 22 DNC 21 DA9

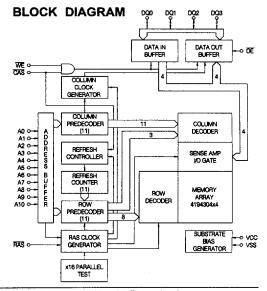

### DESCRIPTION

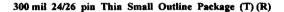

The HY5117404B is the new generation and fast dynamic RAM organized 4,194,304 x 4-bit. The HY5117404B utilizes Hyundai's CMOS silicon gate process technology as well as advanced circuit techniques to provide wide operating margins to the users. Multiplexed address inputs permit the HY5117404B to be packaged in standard 24/26 pin plastic SOJ, TSOP-II and Reverse TSOP-II.

The package size provides high system bit densities and is compatible with widely available automated testing and insertion equipments. System oriented feature includes single power supply of 5V ±10% tolerance and direct interfacing capability with high performance logic families such as Schottky TTL.

### FEATURES

Low power dissipation Max. battery back-up 2.75mW (SL-part) Max. CMOS standby 2.2mW (SL-part) 5.5mW

Max. TTL standby 11.0mW May onerating

| max. Operating |       |  |  |  |  |  |  |

|----------------|-------|--|--|--|--|--|--|

| Speed Power    |       |  |  |  |  |  |  |

| 50             | 798mW |  |  |  |  |  |  |

| 60             | 660mW |  |  |  |  |  |  |

| 70             | 550mW |  |  |  |  |  |  |

- Single power supply of 5V±10%

- TTL compatible inputs and outputs

- · Fast access and cycle time

| Speed | <b>t</b> RAC | <b>t</b> CAC | tHPC |

|-------|--------------|--------------|------|

| 50    | 50ns         | 13ns         | 20ns |

| 60    | 60ns         | 15ns         | 25ns |

| 70    | 70ns         | 18ns         | 30ns |

- Extended data out operation

- Multi-bit test capability

- Read-Modify-Write capability

- CAS-before-RAS, RAS-only, Hidden refresh and Self Refresh capability

- 2048 refresh cycles / 256ms (SL-part) 2048 refresh cycles / 32ms

#### PIN DESCRIPTION

| RAS     | Row Address Strobe    |

|---------|-----------------------|

| CAS     | Column Address Strobe |

| WE      | Write Enable          |

| ŌĒ      | Output Enable         |

| A0-A10  | Address input         |

| DQ0-DQ3 | Data Input/Output     |

| Vcc     | Power (+5V)           |

| Vss     | Ground                |

#### **PIN CONNECTION**

| VCC 1<br>DC 2<br>NCC 3<br>WEC 4<br>RASC 5<br>A110 6             | 26 b VSS<br>25 b Q<br>24 b NC<br>23 b CAS<br>23 b CAS<br>22 b AS<br>21 b AS | VCCd 10                                                            |

|-----------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------|

| NCD 3<br>WED 4<br>RASC 5                                        | 25 00<br>24 0 NC<br>23 0 CAS<br>22 0 NC                                     | VCCU 1 <sub>O</sub><br>DCU 2<br>NCU 3<br>WEU 4<br>RASU 5<br>A110 6 |

| WE 4                                                            | 23 ECAS                                                                     |                                                                    |

| A110 6                                                          | 21 1 49                                                                     | A110 6                                                             |

|                                                                 | <b>F</b> . <b>-</b>                                                         |                                                                    |

| A101 8                                                          | 19 DA8<br>18 DA7                                                            | A100 8<br>A00 9<br>A10 10<br>A20 11<br>A20 12                      |

| A01 9<br>A10 10                                                 | 17 6A6                                                                      | A10 10                                                             |

| A20 11                                                          | 17 0A5<br>16 DA5<br>15 DA4                                                  | A20 11                                                             |

| A100 8<br>A00 9<br>A10 10<br>A20 11<br>A30 12<br>VCC0 13        | 19 0 A8<br>18 0 A7<br>17 0 A5<br>16 0 A5<br>15 0 A4<br>14 0 VSS             | A00 9<br>A10 10<br>A20 11<br>A30 12<br>VCC0 13                     |

|                                                                 | <br>ນ                                                                       | TS                                                                 |

|                                                                 |                                                                             |                                                                    |

| VSS≖26                                                          |                                                                             |                                                                    |

| Qcd 25                                                          |                                                                             |                                                                    |

| 0 a 25<br>NC a 24<br>CAS a 23<br>NC a 22<br>NC a 22             | 3 PNC                                                                       |                                                                    |

| NCm22                                                           | 5 RAS                                                                       |                                                                    |

| A9 @ 21                                                         | 0 1 × VCC<br>2 × D<br>3 × NC<br>4 × WE<br>5 × RAS<br>6 × A11                |                                                                    |

| A8 m 19                                                         | 8 410                                                                       |                                                                    |

| A8 ± 19<br>A7 ± 18<br>A8 ± 17<br>A5 ± 16<br>A4 ± 15<br>VSS ± 14 | 9 p A0<br>10 p A1<br>11 p A2<br>12 p A3<br>13 p VCC                         |                                                                    |

| AD 417<br>A5 61 16                                              | 111 A2                                                                      |                                                                    |

| A4 15                                                           | 12 A3                                                                       |                                                                    |

| VSScc 14                                                        | 13 13 12 VOC                                                                |                                                                    |

Reverse TSOP -II

This document is a general product description and is subject to change without notice. Hyundai Electronics does not assume any responsibility for use of circuits described. No patent licences are implied. 603

4675088 0004628 875 🎟

1AD45-00-MAY95

# ABSOLUTE MAXIMUM RATING

| SYMBOL    | PARAMETER                          | RATING      | UNIT     |

|-----------|------------------------------------|-------------|----------|

| Та        | Ambient Temperature                | 0 to 70     | °C       |

| TSTG      | Storage Temperature                | -55 to 150  | °C       |

| VIN, VOUT | Voltage on Any Pin Relative to Vss | -1.0 to 7.0 | V        |

| Vcc       | Voltage on VCC Relative to Vss     | -1.0 to 7.0 | V        |

| los       | Short Circuit Output Current       | 50          | mA       |

| PD        | Power Dissipation                  | 1.0         | W        |

| TSOLDER   | Soldering Temperature • Time       | 260 • 10    | °C • sec |

NOTE: Operation at or above Absolute Maximum Ratings can adversely affect device reliability.

## **RECOMMENDED DC OPERATING CONDITIONS**

$(TA = 0^{\circ}C \text{ to } 70^{\circ}C)$

| SYMBOL | PARAMETER            | MIN. | TYP. | MAX.    | UNIT |

|--------|----------------------|------|------|---------|------|

| Vcc    | Power Supply Voltage | 4.5  | 5.0  | 5.5     | V    |

| Vih    | Input High Voltage   | 2.4  | -    | Vcc+1.0 | V    |

| VIL    | Input Low Voltage    | -1.0 | -    | 0.8     | V    |

NOTE: All Voltage are referenced to Vss.

### **DC CHARACTERISTICS**

| SYMBOL | PARAMETER                                                                                              | TEST CONDITIONS                                                                          | SPEED/<br>POWER | MIN. | MAX.              | UNIT | NOTE        |

|--------|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------|------|-------------------|------|-------------|

| 111    | Input Leakage Current<br>(Any Input Pins)                                                              | $Vss \le VIN \le Vcc+1.0$ ,<br>All other pins not under test = "                         | Vss             | -10  | 10                | μA   |             |

| ILO    | Output Leakage Current<br>(High impedance State)                                                       | Vss ≤ Vou⊺ ≤ Vcc<br>RAS & CAS at VIH                                                     |                 | -10  | 10                | μA   |             |

| ICC1   | Vcc Supply Current,<br>Operating                                                                       | tRC = tRC (min.)                                                                         | 50<br>60<br>70  | -    | 145<br>120<br>100 | mA   | 1,2,3       |

| ICC2   | Vcc Supply Current,<br>Operating.                                                                      | RAS & CAS at VIH(min.),<br>other inputs ≥ VSS                                            |                 | -    | 2                 | mA   |             |

| ICC3   | Vcc Supply Current,<br>RAS-only refresh                                                                | tRC = tRC (min.)                                                                         | 50<br>60<br>70  | -    | 145<br>120<br>100 | mA   | 1,3         |

| ICC4   | Vcc Supply Current,<br>EDO mode                                                                        | tPC = tPC (min.)                                                                         | 50<br>60<br>70  |      | 130<br>110<br>90  | mA   | 1,2,3       |

| ICC5   | Vcc Supply Current,<br>CMOS Standby                                                                    | RAS & CAS ≤ Vcc-0.2V                                                                     |                 |      | 1<br>0.4          | mA   | 5           |

| ICC6   | Vcc Supply Current,<br>CAS-before- RAS<br>refresh                                                      | tRC = tRC (min.)                                                                         | 50<br>60<br>70  | -    | 145<br>120<br>100 | mA   | 1,3         |

| ICC7   | Vcc Supply Current,<br>Battery Back up                                                                 | $t_{RC} = 125 \mu s$ ,<br>CAS = CBR cycling or 0.2V,                                     | tRAS ≤<br>300ns | -    | 300               | μΑ   | 1,4,5       |

|        | (SL-part only)<br>WE = Vcc-0.2V,<br>A0-A10 = Vcc-0.2V or 0.2V,<br>DQ0-D Q3 = 0.2V, Vcc-0.2V<br>or open |                                                                                          | tRAS ≤<br>1μs   | -    | 500               |      |             |

| ICC8   | Vcc Supply Current<br>Self Refresh<br>(SL-part only)                                                   | RAS & CAS ≤ 0.2V<br>OE & WE & A0-A10= Vcc-0.2V or 0.2V,<br>DQ0-DQ3=Vcc-0.2V,0.2V or open |                 | -    | 300               | μA   | 5           |

| Vol    | Output Low Voltage                                                                                     | IOL = 4.2mA                                                                              |                 | -    | 0.4               | V    | · · · · · · |

| Voн    | Output High Voltage                                                                                    | IOH = -5.0mA                                                                             |                 | 2.4  | -                 | V    |             |

(TA=0°C to 70°C, Vcc=5V±10%, Vss=0V, unless otherwise noted.)

NOTE :

1. ICC1, ICC3, ICC4, ICC6 and ICC7 depend on cycle rates.

2. ICC1, ICC3, ICC4 and ICC6 depend on output loading. Specified values are obtained with the output open.

3. ICC is specified as average current. ICC1, ICC3, ICC6, Address can be changed maximum two times while RAS=VIL. ICC4, Address can be changed maximum once while CAS=VIH.

4. tras(max.)=1µs is only applied to refresh of battery backup but tras(max.)=10µs is applied to normal functional operation.

📕 4675088 0004630 423 🎟

5. ICC5(max.) =0.4mA and ICC7 and ICC8 are applied to SL-parts only.

1AD45-00-MAY95

605

## **AC CHARACTERISTICS**

|    | SYMBOL |                                               | HY5117404BJC/TC/RC/SLJC/SLT/SLRC |      |           |      |                |      |         |           |      |

|----|--------|-----------------------------------------------|----------------------------------|------|-----------|------|----------------|------|---------|-----------|------|

| #  | SYMBOL | PARAMETER                                     | - 50 - 60 - 70                   |      | - 50 - 60 |      | - 50 - 60 - 70 |      | - 70 UN |           | NOTE |

|    |        |                                               | MIN.                             | MAX. | MIN.      | MAX. | MIN.           | MAX. | 1       | 1         |      |

| 1  | tRC    | Random Read or Write Cycle Time               | 84                               | -    | 104       | -    | 124            | -    | ns      | t         |      |

| 2  | tRWC   | Read-Modify-Write Cycle Time                  | 113                              | -    | 137       | -    | 160            | -    | ns      |           |      |

| 3  | tHPC   | EDO Mode Cycle Time                           | 20                               | -    | 25        | -    | 30             | -    | ns      | 15        |      |

| 4  | tHPRWC | EDO Mode Read-Modify-Write Cycle<br>Time      | 61                               | -    | 70        | -    | 78             | -    | ns      | 15        |      |

| 5  | tRAC   | Access Time from RAS                          | -                                | 50   | -         | 60   | -              | 70   | ns      | 4,9,10    |      |

| 6  | tCAC   | Access Time from CAS                          | -                                | 13   | -         | 15   | -              | 18   | ns      | 4.9       |      |

| 7  | taa    | Access Time from Column Address               | -                                | 25   | -         | 30   | -              | 35   | ns      | 4,10      |      |

| 8  | tCPA   | Access Time from CAS Precharge                | -                                | 30   | -         | 35   | -              | 40   | ns      | 4         |      |

| 9  | tCLZ   | CAS to Output Low Impedance                   | 3                                | -    | 3         | -    | 3              | -    | ns      | 4         |      |

| 10 | tCEZ   | Output Buffer Turn-off Delay Time from<br>CAS | 3                                | 13   | 3         | 15   | 3              | 18   | ns      | 5         |      |

| 11 | tT     | Transition Time (Rise and Fall)               | 2                                | 50   | 2         | 50   | 2              | 50   | ns      | 3         |      |

| 12 | tRP    | RAS Precharge Time                            | 30                               | -    | 40        | -    | 50             | -    | ns      |           |      |

| 13 | tRAS   | RAS Pulse Width                               | 50                               | 10K  | 60        | 10K  | 70             | 10K  | ns      |           |      |

| 14 | tRASP  | RAS Pulse Width (EDO Mode)                    | 50                               | 200K | 60        | 200K | 70             | 200K | ns      | · · · · · |      |

| 15 | tRSH   | RAS Hold Time                                 | 13                               | -    | 15        | -    | 18             | -    | ns      |           |      |

| 16 | tCSH   | CAS Hold Time                                 | 40                               | -    | 45        | -    | 50             | -    | ns      |           |      |

| 17 | tCAS   | CAS Pulse width                               | 8                                | 10K  | 11        | 10K  | 14             | 10K  | ns      |           |      |

| 18 | tRCD   | RAS to CAS Delay                              | 18                               | 37   | 20        | 45   | 20             | 52   | ns      | 9         |      |

| 19 | tRAD   | RAS to Column Address Delay Time              | 10                               | 25   | 15        | 30   | 15             | 35   | ns      | 10        |      |

| 20 | tCRP   | CAS to RAS Precharge Time                     | 5                                | -    | 5         | -    | 5              | -    | ns      |           |      |

| 21 | tCP    | CAS Precharge Time                            | 8                                | -    | 10        | -    | 12             | -    | ns      |           |      |

| 22 | tASR   | Row Address Set-up Time                       | 0                                | -    | 0         | -    | 0              |      | ns      |           |      |

| 23 | tRAH   | Row Address Hold time                         | 8                                | -    | 10        | -    | 10             | -    | ns      |           |      |

| 24 | tASC   | Column Address Set-up Time                    | 0                                | -    | 0         | -    | 0              | -    | ns      |           |      |

| 25 | tCAH . | Column Address Hold Time                      | 10                               | -    | 10        | -    | 10             | -    | ns      |           |      |

| 26 | tAR    | Column Address Hold Time from RAS             | 50                               | -    | 50        | -    | 50             | -    | ns      |           |      |

| 27 | tRAL   | Column Address to RAS Lead Time               | 25                               | -    | 30        | -    | 35             | •    | ns      |           |      |

| 28 | tRCS   | Read Command Set-up Time                      | 0                                | -    | 0         | -    | 0              | -    | ns      |           |      |

| 29 | tRCH   | Read Command Hold Time<br>Referenced to CAS   | 0                                | -    | 0         | -    | 0              | -    | ns      | 6         |      |

| 30 | tRRH   | Read Command Hold Time<br>Referenced to RAS   | 0                                | -    | 0         | -    | 0              | -    | ns      | 6         |      |

| 31 | tWCH   | Write Command Hold Time                       | 8                                | -    | 10        | -    | 10             | -    | ns      |           |      |

| 32 | tWCR   | Write Command Hold Time from RAS              | 45                               | -    | 50        | -    | 55             | -    | ns      |           |      |

| 33 | tWP    | Write Command Pulse Width                     | 8                                | -    | 10        | -    | 10             | -    | ns      |           |      |

| 34 | tRWL   | Write Command to RAS Lead Time                | 10                               | -    | 12        | -    | 12             | -    | ns      |           |      |

| 35 | tCWL   | Write Command to CAS Lead Time                | 10                               | -    | 12        | -    | 12             | -    | ns '    |           |      |

| 36 | tDS    | Data-In Set-up Time                           | 0                                | -    | 0         | -    | 0              | -    | ns      | 7         |      |

| 37 | tDH    | Data-In Hold Time                             | 10                               | -    | 10        | -    | 10             | -    | ns      | 7         |      |

| 38 | tDHR   | Data-In Hold Time Referenced to RAS           | 50                               | -    | 50        | -    | 50             | •    | ns      |           |      |

| 39 | tREF   | Refresh Period (2048 cycles)                  | -                                | 32   | •         | 32   | -              | 32   | ms      | 12        |      |

| 40 | twcs   | Write Command Set-up Time                     | -                                | 256  | -         | 256  | -              | 256  | ms      | 11<br>8   |      |

(TA=0°C to 70°C, Vcc=5V ±10%, Vss=0V, unless otherwise noted.)

606

🖬 4675088 0004631 36T 📰

1AD45-00-MAY95

\_\_\_\_

### **AC CHARACTERISTICS**

(continued)

|    |             |                                               | HY5117404BJ/T/R/SLJ/SLT/SLR |           |      |      | R    |      |      |   |

|----|-------------|-----------------------------------------------|-----------------------------|-----------|------|------|------|------|------|---|

| #  | SYMBOL      | PARAMETER                                     | -                           | - 50 - 60 |      | -    | 70   | UNIT | NOTE |   |

|    |             |                                               | MIN.                        | MAX.      | MIN. | MAX. | MIN. | MAX. |      |   |

| 41 | tCWD        | CAS to WE Delay Time                          | 30                          | -         | 34   | -    | 40   | -    | ns   | 8 |

| 42 | tRWD        | RAS to WE Delay Time                          | 67                          | -         | 79   | -    | 92   | -    | ns   | 8 |

| 43 | tAWD        | Column Address to WE Delay Time               | 42                          | -         | 49   | -    | 57   | -    | ns   | 8 |

| 44 | tCSR        | CAS Set-up Time (CBR Cycle)                   | 5                           | -         | 5    | -    | 5    | -    | ns   |   |

| 45 | <b>tCHR</b> | CAS Hold Time (CBR Cycle)                     | 10                          | -         | 10   | -    | 10   | -    | ns   |   |

| 46 | tRPC        | RAS to CAS Precharge Time                     | 5                           | -         | 5    | -    | 5    | -    | ns   |   |

| 47 | tCPT        | CAS Precharge Time (CBR Counter Test)         | 15                          | •         | 20   | -    | 25   | -    | ns   |   |

| 48 | tROH        | RAS Hold Time Reference to OE                 | 10                          | -         | 10   | -    | 10   | -    | ns   |   |

| 49 | tOEA        | OE Access Time                                | -                           | 13        | -    | 15   | -    | 18   | ns   |   |

| 50 | tOED        | OE to Data Delay                              | 13                          | -         | 15   | -    | 18   | -    | ns   |   |

| 51 | tOEZ        | Output Buffer Turn Off Delay Time from OE     | 3                           | 13        | 3    | 15   | 3    | 18   | ns   | 5 |

| 52 | tOEH        | OE Command Hold Time                          | 13                          | -         | 15   | -    | 18   | -    | ns   |   |

| 53 | tCPWD       | WE Delay Time from CAS Precharge              | 47                          | -         | 54   | -    | 62   | -    | ns   | 8 |

| 54 | tRHCP       | RAS Hold Time from CAS Precharge              | 30                          | -         | 35   | -    | 40   | -    | ns   |   |

| 55 | tWRP        | WE to RAS Precharge Time (CBR Cycle)          | 10                          | -         | 10   | -    | 10   | -    | ns   |   |

| 56 | tWRH        | WE to RAS Hold Time (CBR Cycle)               | 10                          | -         | 10   | -    | 10   | -    | ns   |   |

| 57 | twrs        | Write Command Set-up Time<br>(Test Mode In)   | 10                          | -         | 10   | -    | 10   | -    | ns   |   |

| 58 | tWTH        | Write Command Hold Time (Test Mode In)        | 10                          | -         | 10   | -    | 10   |      | ns   |   |

| 59 | tRASS       | RAS Pulse Width (Self Refresh Cycle)          | 100                         | -         | 100  | -    | 100  | -    | ns   |   |

| 60 | tRPS        | RAS Precharge Time (Self Refresh Cycle)       | 90                          | -         | 110  | -    | 130  | -    | ns   |   |

| 61 | tCHS        | CAS Hold Time (Self Refresh Cycle)            | -50                         | - 1       | -50  | -    | -50  | -    | ns   |   |

| 62 | tDOH        | Output Data Hold Time                         | 5                           | -         | 5    | -    | 5    | -    | ns   |   |

| 63 | tREZ        | Output Buffer Turn Off Delay Time<br>from RAS | 3                           | 13        | 3    | 15   | 3    | 18   | ns   | 5 |

| 64 | tWEZ        | Output Buffer Turn Off Delay Time from WE     | 3                           | 13        | 3    | 15   | 3    | 18   | ns   | 5 |

| 65 | tWED        | WE to Data Delay Time                         | 13                          | -         | 15   | -    | 18   | -    | ns   |   |

| 66 | tOEP        | OE Hige Pulse Width                           | 5                           | -         | 5    | -    | 8    | -    | ns   |   |

| 67 | tWPE        | WE Pulse Width (Hyper Page Cycle)             | 5                           | -         | 5    | -    | 8    | -    | ns   |   |

| 68 | tOCH        | OE to CAS Hold Time                           | 0                           | -         | 0    | -    | 0    | -    | ns   |   |

| 69 | tCHO        | CAS Hold Time to OE                           | 5                           | -         | 5    | - 1  | 8    | -    | ns   |   |

1AD45-00-MAY95

Powered by ICminer.com Electronic-Library Service CopyRight 2003

📕 4675088 0004632 2T6 📕 \_\_\_\_\_

607

### AC CHARACTERISTICS IN TEST MODE

#### NOTE 13

608

|    |             |                                                | HY5117404BJC/TC/RC/SLJC/SLTC/SLR |      |         |      |      | ŀ    |      |                                       |

|----|-------------|------------------------------------------------|----------------------------------|------|---------|------|------|------|------|---------------------------------------|

| #  | SYMBOL      | PARAMETER                                      | -50                              |      | -50 -60 |      | -7   | 70   | UNIT | NOTE                                  |

|    |             |                                                | MIN.                             | MAX. | MIN.    | MAX. | MIN. | MAX  | 1    |                                       |

| 1  | tRC         | Random Read or Write Cycle Time                | 95                               | -    | 115     | -    | 135  | -    | ns   | · · · · · · · · · · · · · · · · · · · |

| _2 | tRWC        | Read-Modify-Write Cycle Time                   | 140                              | -    | 160     | -    | 185  | -    | ns   |                                       |

| 3  | tPC         | Fast Page Mode Cycle Time                      | 25                               | -    | 30      | -    | 35   | -    | ns   |                                       |

| 4  | THPRWC      | Fast Page Mode Read-Modify-Write<br>Cycle Time | 70                               | -    | 80      | -    | 90   | -    | ns   |                                       |

| 5  | tRAC        | Access Time from RAS                           | -                                | 55   | -       | 65   | -    | 75   | ns   | 4,9,10                                |

| 6  | tCAC        | Access Time from CAS                           | -                                | 18   | -       | 20   | -    | 23   | ns   | 4.9                                   |

| 7  | tAA         | Access Time from Column Address                | - 1                              | 30   | -       | 35   | -    | 40   | ns   | 4,10                                  |

| 8  | tCPA        | Access Time from CAS Precharge                 | -                                | 35   | -       | 40   | -    | 45   | ns   | 4                                     |

| 13 | tRAS        | RAS Pulse Width                                | 55                               | 10K  | 65      | 10K  | 75   | 10K  | ns   |                                       |

| 14 | tRASP       | RAS Pulse Width (Fast Page Mode)               | 55                               | 200K | 65      | 200K | 75   | 200K | ns   |                                       |

| 15 | tRSH        | RAS Hold Time                                  | 18                               | -    | 20      | -    | 23   | -    | ns   |                                       |

| 16 | tCSH        | CAS Hold Time                                  | 45                               | -    | 50      | -    | 55   | -    | ns   |                                       |

| 17 | tCAS        | CAS Pulse Width                                | 18                               | 10K  | 20      | 10K  | 23   | 10K  | ns   |                                       |

| 27 | tRAL        | Column Address to RAS Lead Time                | 30                               | -    | 35      | -    | 40   | -    | ns   |                                       |

| 41 | tCWD        | CAS to WE Delay Time                           | 40                               | -    | 45      | -    | 50   | -    | ns   | 8                                     |

| 42 | tRWD        | RAS to WE Delay Time                           | 75                               | -    | 90      | -    | 100  | -    | ns   | 8                                     |

| 43 | tawd        | Column Address to WE Delay Time                | 50                               | -    | 60      | -    | 65   | -    | ns   | 8                                     |

| 49 | tOEA        | OE Access Time                                 | -                                | 18   | -       | 20   | -    | 23   | ns   |                                       |

| 50 | tOED        | OE to Data Delay                               | 18                               | -    | 20      | -    | 23   | -    | ns   |                                       |

| 52 | <b>tOEH</b> | OE Command Hold Time                           | 18                               | -    | 20      | -    | 23   | -    | ns   |                                       |

4675088 0004633 132 📖 \_\_\_\_\_

1AD45-00-MAY95

\_\_\_\_.

NOTE:

- 1. An initial pause of 200µs is required after power-up followed by any 8 refresh (RAS only CAS-before-RAS refresh) cycle before proper device operation is achieved.

- If RAS=Vss during power-up, the device could begin an active cycle. These condition results in higher current than necessary which is demanded from the power supply during power-up. It is recommended that RAS and CAS track with Vcc during power-up or be held at a valid VIH in order to minimize the power-up current.

- VIH(min.) and VIL(max.) are reference levels for measuring timing of input signals. Also, transition times are measured between VIH(min.) and VIL(max.), and are assumed to be 5ns for all inputs.

- 4. Measured at VOH=2.0V and VOL=0.8V with a load equivalent to 2 TTL loads and 100pF.

- These parameters define the time at which the output achieves the open circuit condition and is not referenced to output voltage levels.

- 6. Either tRCH or tRRH must be satisfied for a read cycle.

- 7. These parameters are referenced to CAS leading edge in early write cycles and WE leading edge in Read-Modify-Write cycles.

- 8. twcs, tRwD, tcwD, tAWD and tCPWD are not restrictive operating parameters. They are included in the data sheet as electrical characteristics only. If twcs ≥ twcs(min.), the cycle is an early write cycle and data out pin will remain open circuit (high impedance) through the entire cycle. If tRWD≥tRWD(min.), tcWD≥tCWD(min.), tAWD ≥ tAWD(min.), and tCPWD ≥ tCPWD(min.), the cycle is a Read-Modify-Write cycle and data out will contain data read from the selected cell. If neither of the above sets of conditions is satisfied, the condition of the data out (at access time) is indeterminated.

- Operation within the tRCD(max.) limit insures that tRAC(max.) can be met. tRCD(max.) is specified as a reference point only. If tRCD is greater than the specified tRCD(max.) limit, then access time is controlled by tCAC.

- 10.Operation within the tRAD(max.) limit insures that tRAC(max.) can be met. tRAD(max.) is specified as a reference point only. If tRAD is greater than the specified tRAD(max.) limit, then access time is controlled by tAA.

- 11.tREF(max.)=256ms is applied to SL-Parts (HY5117404BSLJ, HY5117404BSLT and HY5117404BSLR).

- 12.A burst of 2048 CAS-before-RAS refresh cycles must be executed within 64ms(256ms for SL-part) after exiting self refresh.

- 13. These specifications are applied to the test Mode.

- 14.If RAS goes high before CAS high going, the open circuit condition is achieved by CAS high going. If CAS goes high before RAS high going, the open circuit condition of the output is achieved by RAS high going.

- 15.tASC ≥ tCP (min.), Assume tT= 2ns

### CAPACITANCE

(TA=25°C, Vcc=5V±10%, Vss=0V, f=1MHz, unless otherwise noted.)

| SYMBOL | PARAMETER                               | TYP. | MAX. | UNIT |

|--------|-----------------------------------------|------|------|------|

| CIN1   | Input Capacitance (A0-A10)              | -    | 5    | pF   |

| CIN2   | Input Capacitance (RAS,CAS, WE, OE)     | -    | 7    | pF   |

| CDQ    | Data Input/Output Capacitance (DQ0-DQ3) | -    | 7    | pF   |

1AD45-00-MAY95

4675088 0004634 079

609

# ·\* YUNDAI

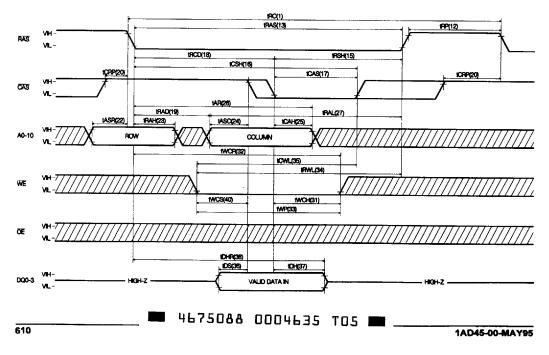

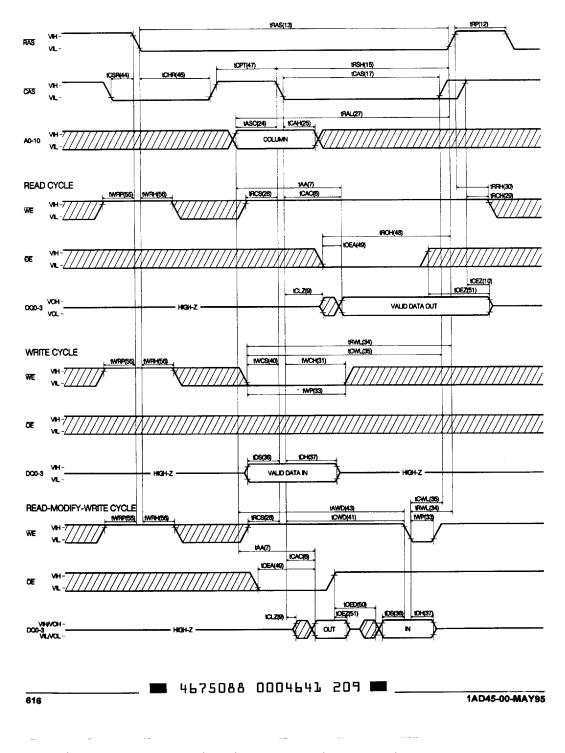

### TIMING DIAGRAM

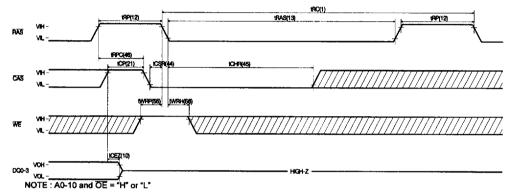

#### **READ CYCLE**

#### EARLY WRITE CYCLE

WRITE CYCLE (OE CONTROLLED WRITE)

**READ-MODIFY-WRITE CYCLE**

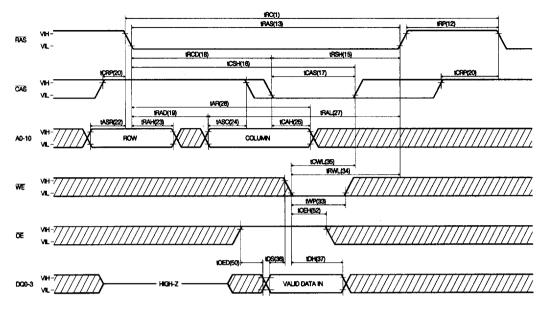

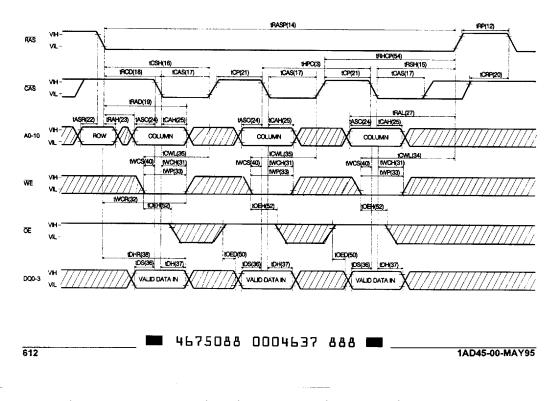

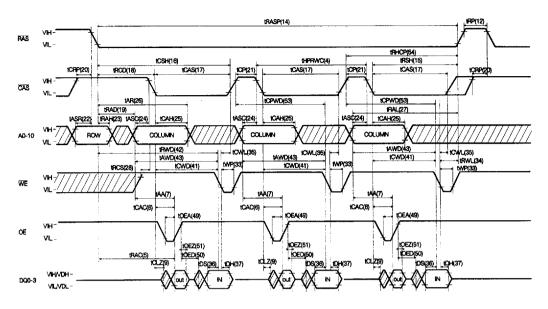

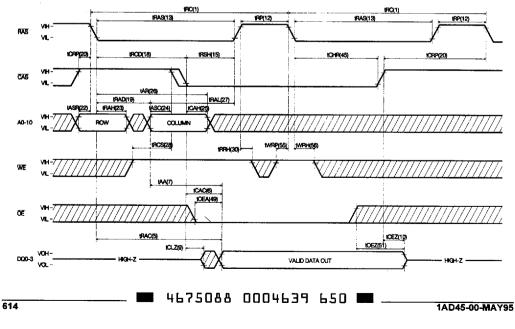

#### EDO MODE READ CYCLE

EDO MODE EARLY WRITE CYCLE

Powered by ICminer.com Electronic-Library Service CopyRight 2003

EDO MODE READ-MODIFY-WRITE CYCLE

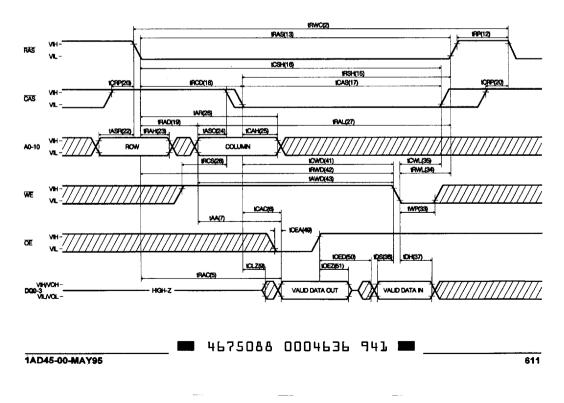

EDO MODE READ AND WRITE MIXED CYCLE

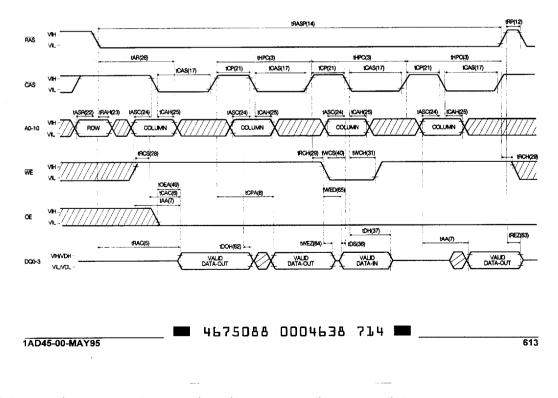

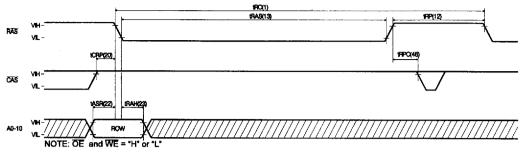

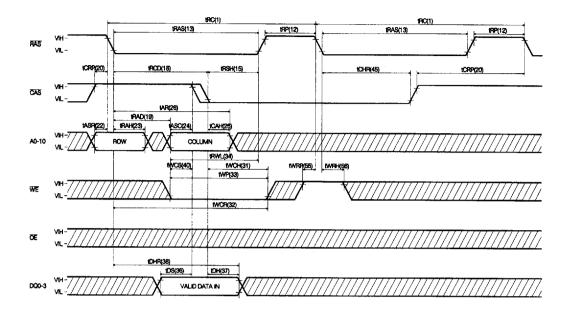

#### **RAS-ONLY REFRESH CYCLE**

#### **CAS-BEFORE-RAS REFRESH CYCLE**

### HIDDEN REFRESH CYCLE (READ)

### HIDDEN REFRESH CYCLE (WRITE)

### **CAS-BEFORE-RAS SELF REFRESH CYCLE**

CAS-BEFORE-RAS REFRESH COUNTER TEST CYCLE

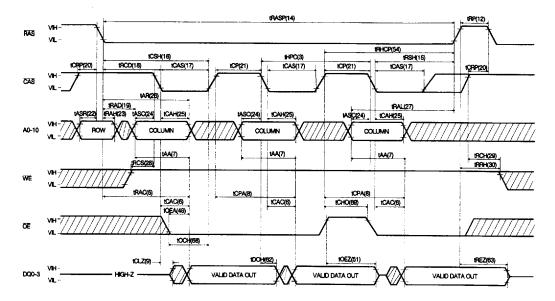

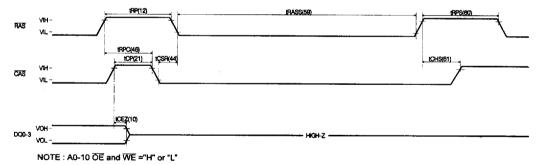

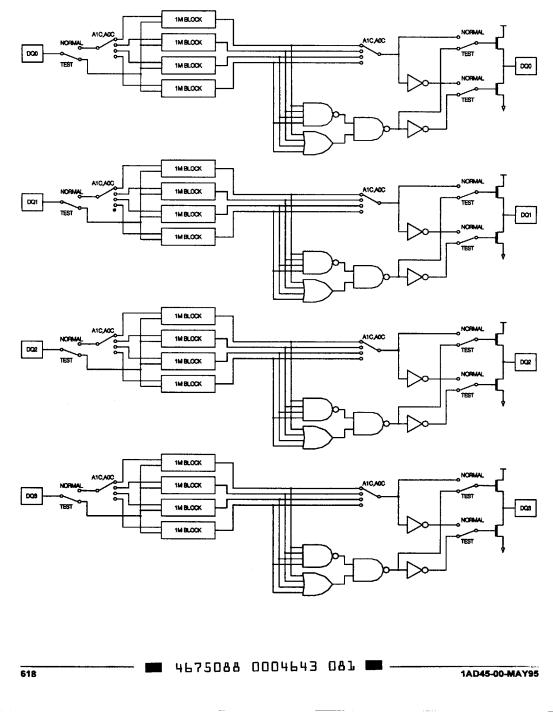

### TEST MODE

The HY511704B is a DRAM organized 4,194,304 x 4-bit. It is internally organized 1,048,576 x 16-bit. In Test Mode, data are written into 16 sectors (Each is composed of 1M bits) in parallel and retrieved the same way. Column address A0 and A1 are not used. If, upon reading, 4-bit data from 4 sectors connected to one DQ pin are equal (all "1"s or "0"s), the DQ pin indicates a "1". If they are not equal, the DQ pin indicates a "0". Belowing shows the timing diagram of the HY5117404B to enter Test Mode. In Test Mode, the 4M x 4 DRAM can be tested as if it were a 1M x 4 DRAM. WE, CAS-before-RAS cycle (Test Mode In Cycle) puts the HY5117404B into Test Mode, and CAS-before-RAS or RAS-only refresh cycle puts it back into Normal Model. In Test Mode, WE, CAS-before-RAS cycle shall be used for the refresh operation. The Test Mode function refuces test time(1/4 in case of N test pattern).

#### (BC(1) 19P(12) (PAS(13) #RP(12) RAS 1FIPC(48) 1CSR( 1018(45) (CP(21)) CAS WTS(57) WTH(58 WF ICEZ(10) VOH DQ0-3 HGH-Z ŝ

#### TEST MODE IN CYCLE

**BLOCK DIAGRAM IN TEST MODE**

### PACKAGE INFORMATION

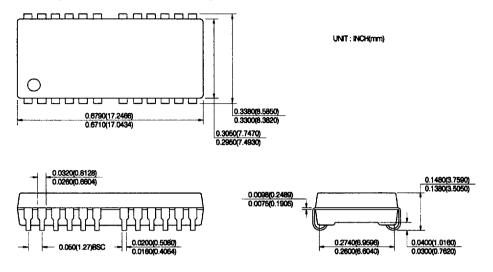

#### 300 mil 24/26 pin Small Outline J-form Package (J)

### ORDERING INFORMATION

| PART NUMBER   | SPEED    | POWER   | PACKAGE    |

|---------------|----------|---------|------------|

| HY5117404BJ   | 50/60/70 |         | SOJ        |

| HY5117404BLJ  | 50/60/70 | SL-part | SOJ        |

| HY5117404BAT  | 50/60/70 |         | TSOP-II    |

| HY5117404BSLT | 50/60/70 | SL-part | TSOP-II    |

| HY5117404BR   | 50/60/70 |         | TSOP-II(R) |

| HY5117404BSLR | 50/60/70 | SL-part | TSOP-II(R) |