# GM82C803A/B

FDC, UARTS with FIFO, EPP/ECP, IDE Controller

# General Description

The GM82C803A/B chip replaces with a single 100 pin chip, a floppy disk controller (FDC) with data separator, two UARTs(GM16C550), one IEEE 1284 parallel port. The GM82C803A/B also includes one game port chip select, hard disk controller interface and standard AT address decoding for on-chip function. The floppy disk control part provides all the needed functionality between the host processor peripheral bus and the cable connector to the floppy disk driver. It integrates the function of the formatter/controller, data separator, write, precompensation, data rate selection, clock generation and high current drivers and supports the 4MB drive as well as the other standard drives. The UARTs perform the parallel to serial/serial to parallel conversion on the data characters received from the CPU or Modem. The IEEE 1284 parallel port is full compatible with the new IEEE 1284 standard. Configuration registers can be used to enable or disable any on-chip function independently of the others.

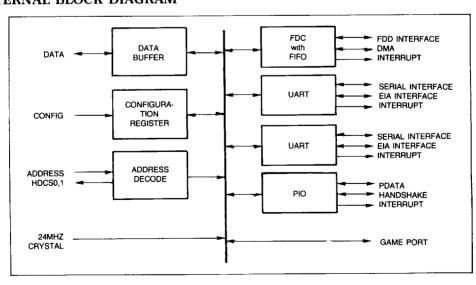

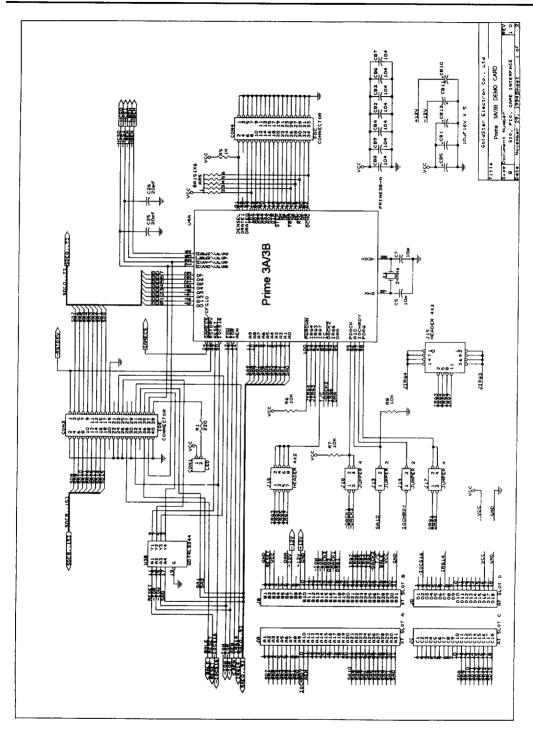

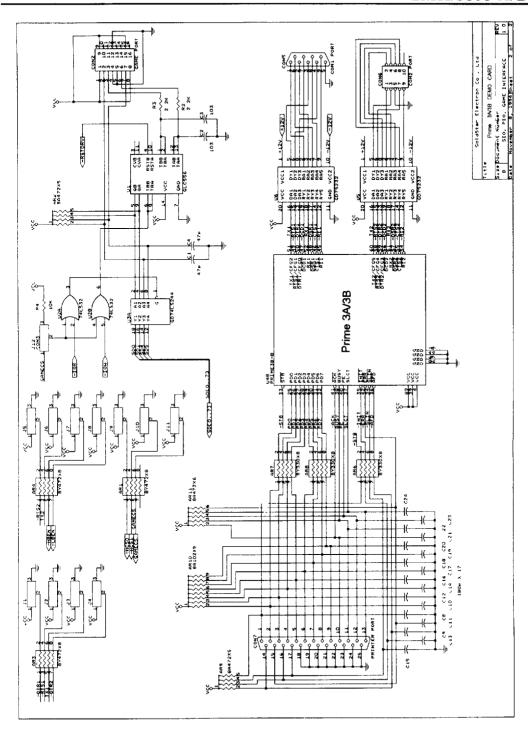

# INTERNAL BLOCK DIAGRAM

# **Features**

- 100% hardware and software compatible to the IBM PC/AT

- Floppy disk controller with 16byte FIFO (default disable)

- 100% compatible to the 765B architecture

- FDD SWAP

- Data rate up to 1Mbps

- Perpendicular recording drive support

- Drives up to four FDD

- 48mA floppy disk drive interface

- Dual UART compatible to the GM16C550

- MIDI interface

- · 16 byte transmitter and receiver FIFO

- Programmable character lengths (5,6,7,8)

- Even, odd, stick or no parity bit generation and detection

- Independent transmit and receive control

- IDE interface

- Additional PIO Mode (Prime 3B only)

- ECP (IEEE1284)

- EPP (Version 1.9: Default, Version 1.7)

- One game chip select

- · Low power mode

- Fabricated in GS's 0.8μm DLM CMOS technology

- 100-pin POFP

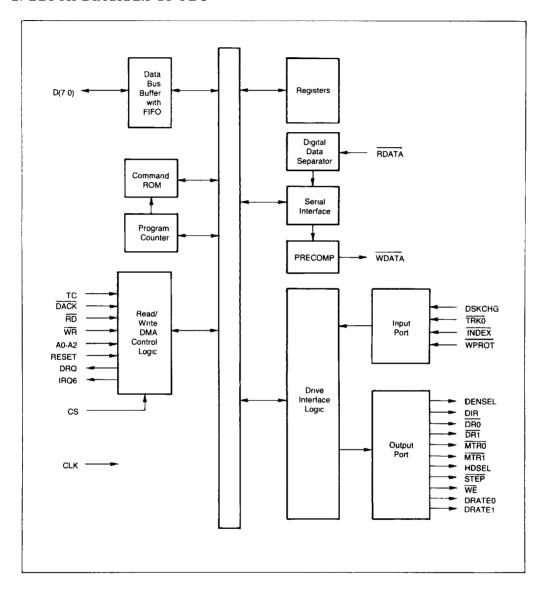

# 2. BLOCK DIAGRAM OF FDC

# GoldStar

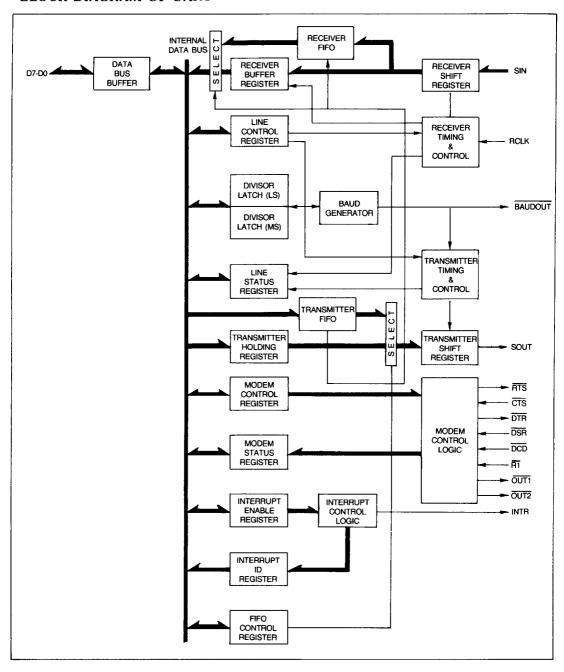

# **BLOCK DIAGRAM OF UART**

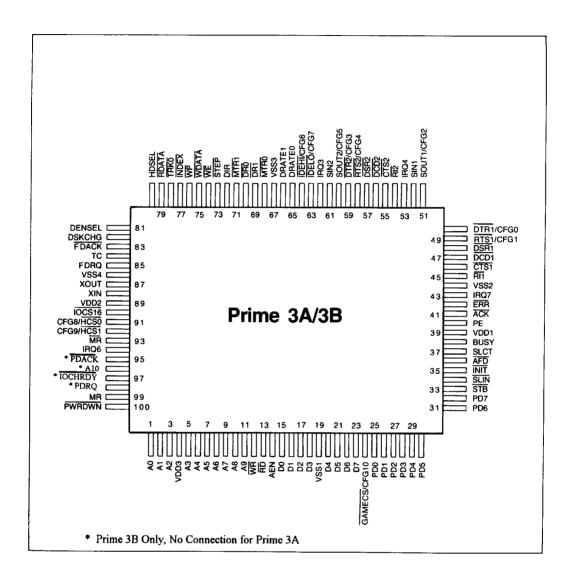

# 3. PIN DESCRIPTIONS

# (1) Host Interface

| Pin No         | Pin Name      | I/O | Description                                                                                                                                                                                                                                                                                                        |  |

|----------------|---------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 53             | IRQ4          | 0   | This active high output is serial port (assigned as COM1) interrupt. See PIN 62 (IRQ3).                                                                                                                                                                                                                            |  |

| 62             | IRQ3          | 0   | This active high output is serial port [assigned as COM2] interrupt. It goes high whenever enabled via the IER and any of following serial interrupt conditions are active: Receiver Error Flag set, Receiver Empty or Modem Status Set. The interrupt is reset low upon appropriate service or a reset operation. |  |

| 94             | IRQ6          | 0   | This active high output indicates that the completion of command execution or data transfer requests (in non-DMA mode) during FDC operation.                                                                                                                                                                       |  |

| 43             | IRQ7          | 0   | This active high output is parallel port interrupts. When enabled (Control Register bit 4=1), the appropriate interrupt signal will follow the ACK signal input.                                                                                                                                                   |  |

| 11-5<br>3-1/96 | A9-A0<br>/A10 | I   | The address lines select the internal registers during CPU bus operation.                                                                                                                                                                                                                                          |  |

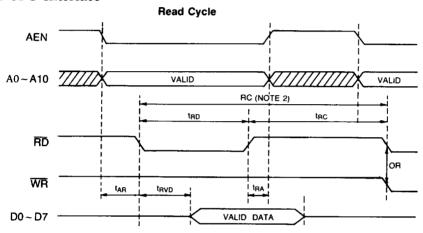

| 14             | AEN           | I   | This active high input disables address selection.                                                                                                                                                                                                                                                                 |  |

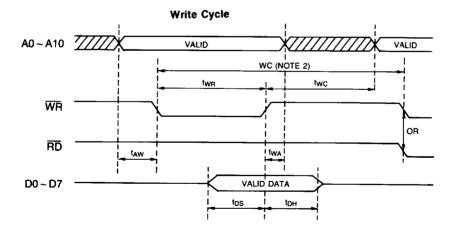

| 13             | RD            | 1   | This active low input is a control signal for transfer of data or status onto the data bus by the GM82C803A/B.                                                                                                                                                                                                     |  |

| 12             | WR            | I   | This active low input is a control signal for latching data from the bus into the selected internal register.                                                                                                                                                                                                      |  |

| 99             | MR            | 1   | This active high input clears registers. In FDC, it clears device outputs, sets data rate to 250 kb/s. UART goes into an idle mode in which all serial data activities are suspended.                                                                                                                              |  |

| 93             | MR            | 0   | This active low output is reset signal. It is used for IDE interface.                                                                                                                                                                                                                                              |  |

| 15-18<br>20-23 | D0-D7         | I/O | The Data Bus provides eight 3-state I/O lines for the transfer of data, control and status information between GM82C803A/B and CPU.                                                                                                                                                                                |  |

| 97             | TOCHRDY       | 0   | In EPP mode, this pin is pulled low to extended the read, write command.                                                                                                                                                                                                                                           |  |

| 84             | TC            | I   | This active high input indicates the termination of a DMA transfer. TC will be qualified by DACK.                                                                                                                                                                                                                  |  |

| 100            | PWRDWN        | I   | This active low input will stop the clocks and make outputs Hi-Z state.                                                                                                                                                                                                                                            |  |

| 98             | PDRQ          | 0   | This active high output requests the DMA controller to transfer data. This signal is enabled by the bit 3 of Extended Control Register (ECR).                                                                                                                                                                      |  |

| 95             | PACK          | I   | This active low input is used by the DMA controller to trnsfer date from the GM82C803A/B onto the data bus. This signal is enabled by the bit 3 of Extended Control Register (ECR).                                                                                                                                |  |

# (2) Serial Interface

| Pin No | Pin Name | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                               |  |

|--------|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 51     | SOUT1    | 0   | This output signal is serial data out from the UART's transmitter circuitry after reset or after 00H is written to the IIR. It is set to the Marking (logic 1) state upon a reset operation.                                                                                                                                                                                                              |  |

|        | BOUT1    | 0   | This output provides the associated serial channel Baudout signal, after data 10H has been written to the IIR.                                                                                                                                                                                                                                                                                            |  |

|        | CFG2     | I   | During rest, this input determines UART1 enable.                                                                                                                                                                                                                                                                                                                                                          |  |

| 46     | CTSI     | I   | This active low input is a Modem status input and indicates that the modem has data to send. The CPU can test its condition by reading bit 4 of MSR. Bit 0 of MSR indicates whether this input has changed state since the previous reading of the MSR. It has no effect on the transmitter. If this signal changes state with the Modem status interrupt enabled, an interrupt is generated.             |  |

| 48     | DSRT     | I   | This active low input means that the Modem is ready to establish the communication link with the UART. This input is a Modem status input and reflected in bit 5 of Modem Status Register (MSR). Bit 1 of MSR indicates whether this signal has changed state since the previous reading of the MSR. It this signal change state with the Modem status interrupt enabled, an interrupt is generated.      |  |

| 50     | DTR1     | 0   | This active low output indicates that the UART is ready to establish a communication link. This pin is set low by writing high to bit 0 of MCR. This pin is inactive (high) after reset.                                                                                                                                                                                                                  |  |

|        | CFG0     | I   | During reset, this input determines IDE enable.                                                                                                                                                                                                                                                                                                                                                           |  |

| 49     | RTS1     | 0   | This active low output indicates that the UART has data ready to transmit. This pin is set to low by writing a logic 1 to bit 1 of Modem Control Register (MCR). This pin is inactive (high) after reset.                                                                                                                                                                                                 |  |

|        | CFG1     | I   | During reset, this input determines FDC enable.                                                                                                                                                                                                                                                                                                                                                           |  |

| 45     | RII      | I   | This active low input is Modem status input and indicates that telephone ringing signal has been received by the Modem. The CPU can test its condition by reading bit 6 of MSR. Bit 2 of MSR indicates whether this input has changed from high to low since the previous reading of the MSR. If this signal changes from high to low with the Modem status interrupt enabled, an interrupt is generated. |  |

| 52     | SIN 1    | · I | This input receives serial data from the communication line or Modem.                                                                                                                                                                                                                                                                                                                                     |  |

# (2) Serial Interface

| Pin No | Pin Name | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|--------|----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 47     | DCD1     | I   | This active low input indicates that the data carrier has been detected by the Modem. This is Modem input whose condition can be tested by the CPU by reading bit 7 of MSR. Bit 3 of MSR indicates whether this input has changed since the previous reading of the MSR. It has no effect on the receiver. If this signal changes state with the Modem status interrupt enabled, an interrupt is generated. |  |

| 60     | SOUT2    | 0   | See PIN 51 (SOUT1)                                                                                                                                                                                                                                                                                                                                                                                          |  |

| !      | CFG5     | I   | During reset, this input determines state of configuration bit 5.                                                                                                                                                                                                                                                                                                                                           |  |

| 55     | CTS2     | I   | See PIN 46 (CTS1)                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 57     | DSR2     | I   | See PIN 48 (DSR1)                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 59     | DTR2     | 0   |                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|        | CFG3     | I   | During reset, this input determines UART2 enable.                                                                                                                                                                                                                                                                                                                                                           |  |

| 58     | RTS2     | 0   | See PIN 49 (RTS1)                                                                                                                                                                                                                                                                                                                                                                                           |  |

|        | CFG4     | I   | During reset, this input determines state of configuration bit 4.                                                                                                                                                                                                                                                                                                                                           |  |

| 54     | RI2      | I   | See PIN 45 (RII)                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 61     | SIN2     | I   | See PIN 52 (SIN1)                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 56     | DCD2     | 1   | See PIN 47 (DCD1).                                                                                                                                                                                                                                                                                                                                                                                          |  |

# (3) Parallel Port Interface

| Pin No | Pin Name | I/O | Description                                                                                  |  |

|--------|----------|-----|----------------------------------------------------------------------------------------------|--|

| 32-25  | PD7-PD0  | I/O | These bidirectional pins provide a byte wide input or output port to the system.             |  |

| 37     | SLCT     | I   | This active high input means that the printer is selected.                                   |  |

| 33     | STB      | 0   | This active low output indicates to the printer that the data at the parallel port is valid. |  |

| 34     | SLIÑ     | 0   | This active low output selects the printer.                                                  |  |

| 40     | PE       | I   | This active high input means that the printer is out of paper.                               |  |

| 36     | ĀFD      | 0   | This active low output makes the printer to line feed automatically after each line printed. |  |

| 38     | BUSY     | I   | This active high input means that the Printer has a local operation in progress.             |  |

| 42     | ERR      | 0   | This active low input means that the printer has detected an error.                          |  |

| 35     | ĪNIT     | 0   | This active low output initializes the printer.                                              |  |

| 41     | ĀCK      | I   | This active low input means that the printer has received data.                              |  |

# (4) IDE Interface

| Pin No | Pin Name | I/O | Description                                                                                                                        |  |

|--------|----------|-----|------------------------------------------------------------------------------------------------------------------------------------|--|

| 63     | IDELO C  |     | This active low output enables the low byte data latch during a read or write to the hard drive.                                   |  |

|        | CFG7     | I   | During reset, this input determines UART1 address range.                                                                           |  |

| 64     | IDEHI    | 0   | This active low output enables the high byte data latch during a read or write to the hard drive if the hard drive returns IOCS16. |  |

|        | CFG6     | I   | During reset, this input determines UART2 address range.                                                                           |  |

| 91     | HCS0     | 0   | This active low output provides a harddisk enable signal.                                                                          |  |

|        | CFG8     | I   | During reset, this input determines FDC address range.                                                                             |  |

| 92     | HCS1     | 0   | In AT application, this active low output provides a harddisk enable signal.                                                       |  |

|        | CFG9     | I   | During reset, this input determines IDE address range.                                                                             |  |

| 90     | IOCS16   | I   | This active low input is driven by the peripheral device when it can accommodate a 16-bit access.                                  |  |

# (5) FDD Interface

| Pin No | Pin Name | I/O | Description                                                                                                                                                                                                                |  |

|--------|----------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 81     | DENSEL   | 0   | This output indicates whether a low (250/300 Kbps) or high (500 Kbps/1 Mbps) data rate has been selected.                                                                                                                  |  |

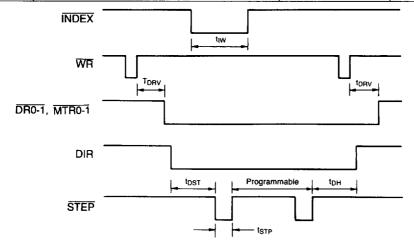

| 72     | DIR      | 0   | This open drain output indicates the direction of the head movement. Logic 0=step in, logic 1=step out.                                                                                                                    |  |

| 66, 65 | DRATE1,0 | 0   | This outputs reflect the contents of bits 1, 0 of the Control Register.                                                                                                                                                    |  |

| 69, 70 | DR1, 0   | 0   | These open drain outputs select drive 1 and drive 0. They are ANDed with the corresponding motor enable lines. These pins contain encoded drive select information if Bit 7 of the Function Selection Register is logic 1. |  |

| 82     | DSKCHG   | 1   | This active high input indicates that the disk drive door has been opened. The active high state of this input is read from bit D7 of I/O address 3f7H.                                                                    |  |

| 77     | INDEX    | I   | This active low input indicates the beginning of a track.                                                                                                                                                                  |  |

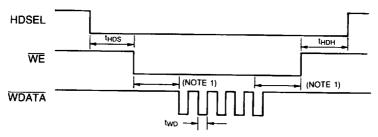

| 80     | HDSEL    | 0   | This open drain output indicates which disk drive head is active. Logic 0=Head 1, logic 1 (open) = Head 0.                                                                                                                 |  |

| 79     | RDATA    | I   | This input is the raw serial bit stream from the disk drive.                                                                                                                                                               |  |

| 71,68  | MTR1,0   | 0   | These open drain outputs enable drive 1 and drive 0. These pins contain encoded drive select information if Bit 7 of the Function Selection Register is logic 1.                                                           |  |

| 73     | STEP     | 0   | This active low output signal issues pulses to the disk drive<br>at a software programmable rate to move the head during a<br>seek operation.                                                                              |  |

| 78     | TRKO     | I   | This active low input indicates that the head is at track 0.                                                                                                                                                               |  |

| 75     | WDATA    | 0   | This open drain output is write precompensated serial data to be written onto the selected disk drive.                                                                                                                     |  |

| 74     | WE       | 0   | This open drain output becomes true just prior to writing on the diskette. This allows current to flow through the write head.                                                                                             |  |

| 76     | WP       | I   | This active low input indicates that the diskette is write protected.                                                                                                                                                      |  |

| 85     | FDRQ     | 0   | This active high output requests the DMA controller to transfer data. This signal is enabled by the bit 3 of Operation Register.                                                                                           |  |

| 83     | FACK     | I   | This active low input is used by the DMA controller to transfer data from the GM3104F onto the data bus. This signal is enabled by the bit 3 of Operation Register.                                                        |  |

# (6) Game Interface

| Pin No | Pin Name | I/O | Description                                                      |

|--------|----------|-----|------------------------------------------------------------------|

| 24     | GAMECS   | 0   | This is the game port chip select output-active low.             |

|        | CFG10    | I   | During reset, this input determines Parallel port address range. |

# (7) Power and Ground

| Pin No | Pin Name | I/O | Description                                                                                                             |

|--------|----------|-----|-------------------------------------------------------------------------------------------------------------------------|

| 39     | VDD1     | P   | +5V DC digital power supply                                                                                             |

| 89     | VDD2     | P   | +5V DC digital power supply                                                                                             |

| 4      | VDD3     | P   | +5V DC digital power supply                                                                                             |

| 19     | VSS1     | G   | 0V Reference                                                                                                            |

| 44     | VSS2     | G   | 0V Reference                                                                                                            |

| 67     | VSS3     | G   | 0V Reference                                                                                                            |

| 86     | VSS4     | G   | 0V Reference                                                                                                            |

| 88     | XIN      | I   | One side of an external 24Mhz crystal is attached here. An external clock is required if crystal is not used.           |

| 87     | XOUT     | 0   | One side of an external 24Mhz crystal is attached here. If an external clock is used, this pin should not be connected. |

# 4. FUNCTIONAL DESCRIPTIONS

# 4.1 Configuration Register

The GM82C803A/B has six byte-wide configuration registers. These Registers are called Function Selection Register (FSR), Address Selection Register (ASR), Power Down Register (PDR), Test Mode Register [TMR], Miscellaneous Function Register (MFR) and ECP Register, respectively. The FSR enables or disables each functional blocks such as FDC, UART1, UART2, PIO, IDE and Game Port. The ASR selects the I/O address ranges of these blocks. The PDR controls the Power Down Mode for the portable system applications. The TMR is used to enhance chip testability.

The configuration registers can be programmed via hardware or software. The states of the 11 configuration pins determine the default value of these registers during system reset. This defines the setting of all configuration registers via hardware. An index and data register pair is used to read and write these registers. Each configuration register is pointed to by the value loaded into the index register. The data to be written into the configuration register is transferred via the data register. Reading a configuration register is done in a similar way. The I/O addresses of the index and data register are 398H and 399H, and the indexes of the six registers are A0, A1, A2, A3, A4 and A5, respectively.

Table 4-1. Index and Data Register I/O Address

| Register | I/O Address | Index      |

|----------|-------------|------------|

| Index    | 398         |            |

| Data     | 399         |            |

| FSR      |             | A0         |

| ASR      |             | A1         |

| PDR      |             | A2         |

| TMR      |             | A3         |

| MFR      |             | A4         |

| ECP      |             | <b>A</b> 5 |

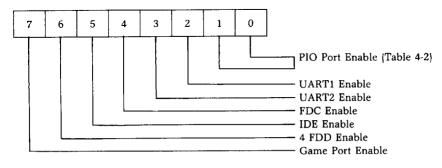

# 4.1.1 Function Selection Register (FSR)

Index = A0

Bit (7:2) are active high enable.

Table 4-2. PIO Port Function Selection

| D1 | D0 | PIO Port Enable  |

|----|----|------------------|

| 0  | 0  | Bidirection Mode |

| 0  | 1  | ECP (Prime 3B)   |

| 1  | 0  | EPP (Prime 3B)   |

| 1  | 1  | PIO Disable      |

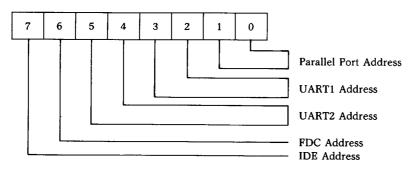

# 4.1.2 Address Selection Register (ASR)

Index = A1

This register selects the ISA I/O address range to which each peripheral function will respond.

Table 4-3. Parallel Port Address Selection

| D1 | D0 | LPT Address Range |

|----|----|-------------------|

| 0  | 0  | LPT2 (378-37F)    |

| 0  | 1  | LPT3 (278-27F)    |

| 1  | Х  | LPT1 (3BC-3BE)    |

Table 4-4. UART1 Address Selection

| D3 | D2 | COM Address Range |

|----|----|-------------------|

| 0  | 0  | COM1 (3F8 — 3FF)  |

| 0  | 1  | COM2 (2F8 — 2FF)  |

| 1  | 0  | COM3 (3E8 - 3EF)  |

| 1  | 1  | COM4 (2E8 — 2EF)  |

Table 4-6. FDC Address Selection

| D6  | FDC Address Range |

|-----|-------------------|

| 0   | 3F0 — 3F7         |

| . 1 | 370 — 377         |

Table 4-5. UART2 Address Selection

| D5 | D4 | COM Address Range |

|----|----|-------------------|

| 0  | 0  | COM1 (3F8 — 3FF)  |

| 0  | 1  | COM2 (2F8 - 2FF)  |

| 1  | 0  | COM3 (3E8 — 3EF)  |

| 1  | 1  | COM4 (2E8 - 2EF)  |

Table 4-7. IDE Address Selection

| D7 | IDE Address Range   |

|----|---------------------|

| 0  | 1F0 — 1F7, 3F6, 3F7 |

| 1  | 170 — 177, 376, 377 |

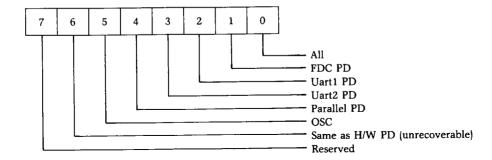

# 4.1.3 Power Down Register (PDR)

Index = A2

# 4.1.4 Test Mode Register (TMR)

This register is used to support chip debugging and testing. The system should not access this register.

Index = A3

Data = 00

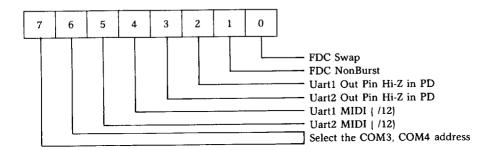

# 4.1.5 Miscellaneous Function Register (MFR)

Index = A4

| 7 6 | СОМЗ  | COM4  |

|-----|-------|-------|

| 0.0 | 3E8-F | 2E8-F |

| 0 1 | 338-F | 238-F |

| 10  | 2E8-F | 2E0-F |

| 11  | 220-7 | 228-F |

(Default)

Table 4-8. COM3, 4 Address

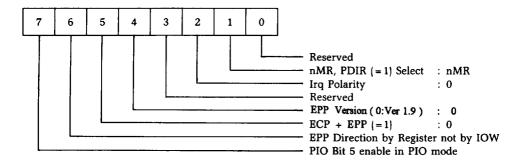

# 4.1.6 ECP Register

Index = A5

# 4.1.7 Hardware Configuration

The eleven configuration pins (CFG0 - 10) determine the default values of FSR and ASR during system reset. CFG0-5 are used for FSR and CFG6-10 are used for ASR. After system reset, the system can modify the configuration registers by software. Table 4-7 shows the hardware configuration of FSR. The default value of the bit 6 (4 FDD select) and the bit 7 (Game Enable) of FSR are 0 (Disable) and 1 (Enable), respectively. And the default values of PDR and TMR are 00H.

Table 4-9. Hardware Configuration of FSR

| CFG pin | Enabled Functions |

|---------|-------------------|

| 0       | IDE Enable        |

| 1 1     | FDC Enable        |

| 2       | UART2 Enable      |

| 3       | UART1 Enable      |

CFG pin (3:0) are active high enable.

Table 4-10. PIO Hardware Configuration

| CFG 5 | CFG 4 | PIO Port Enable  |

|-------|-------|------------------|

| 1     | 1     | Bidirection Mode |

| 1     | 0     | ECP (Prime3B)    |

| 0     | 1     | EPP (Prime3B)    |

| 0     | 0     | PIO Disable      |

Table 4-11. UART1 Hardware Configuration

# Table 4-12. UART2 Hardware Configuration

| CFG6 | UART1 Address    |

|------|------------------|

| 1    | COM1 (3F8 — 3FF) |

| 0    | COM3 (3E8 - 3EF) |

| CFG7 | UART2 Address    |

|------|------------------|

| 0    | COM2 (2F8 - 2FF) |

| 0    | COM4 (2E8 - 2EF) |

Table 4-13. FDC Hardware Configuration

Table 4-14. IDE Hardware Configuration

| CFG8 | FDC Address           |

|------|-----------------------|

| 1    | Primay (3FO - 3F7)    |

| 0    | Secondary (370 - 377) |

| CGF9 | IDE Address                  |

|------|------------------------------|

| 0    | Primary (1F0 - 1F7, 3F6-7)   |

| 0    | Secondary (170 - 177, 376-7) |

Table 4-15. Parallel Port Address Hardware Configuration

| CFG10 | Parallel Port Address |  |

|-------|-----------------------|--|

| 1     | LPT2 (378-37F)        |  |

| 0     | LPT3 (278 — 27F)      |  |

# 4.1.8 S/W configuration procedure

Configuration is accomplished in three basic steps:

- 1. Enter configuration mode

- 2. Configure the GM82C803A/B

- 3. Escape from configuration mode

Any deviation from this sequence causes the configuration state machine to return to its initial idle state. The configuration procedure is intentionally complicated to prevent an errant program from making accidental changes to the chip configuration.

Enter Configuration Mode

Write two consecutive writes of value 33h to port 398h.

The following is an example in 8086 assembly language:

MOV DX, 398h : Port Address

MOV AL, 33h : Data

OUT DX, AL

OUT DX, AL: In configuration mode

Cnfigure the Chip

The six configuration registers can be written to or read.

To read or write data to the registers:

1. Write index to port 398h

2. Write data to port 399h

(where "data" is the data to be written into the register that port 398h points to)

Escape from Configuration Mode

Write cch to port 398h.

The following is an example

MOV DX,398h : Port Address

MOV AL,cch : Data

OUT DX,AL : Exit from configuration mode

# 4.2 Floppy Disk Controller

The FDC contains the circuitry and control functions for interfacing a processor to 4 Floppy Disk Drives. The FDC is capable of supporting either IBM3740 single density format(FM), or IBM system 34 double density format (MFM) including double sided recording. It simplifies and handles most of the burdens associated with implementing a Floppy Disk Drive Interface. It supports data rates of 250/300/500 Kb/s and 1Mb/s. This block integrates; Formatter/Controller, Data Separation, Write Precompensation, Data Rate Selection, Clock Generation, Drive interface drivers and receivers.

It has five registers which may be accessed by the main system processor; a main status register(MSR), a data rate selection register(DSR), a data register(DR), a control register(CR), and a operations register(OR). The main status register contains the status information of the FDC, and may be accessed at any time. The data rate selection register is used to program the data rate, amount of write precompensation, power down mode, and software reset. The data register (actually consists of several registers in a stack with only one register presented to the data bus at a time) stores data, commands, parameters, and FDD status information. Data bytes are read out of, or written into the data register in order to program or obtain the results after execution of a command. The status register may only be read and is used to facilitate the transfer of data between the processor and FDC.

Table 4-16. Register Description and Address

| Address<br>(Hex) | R/W | Register                       |

|------------------|-----|--------------------------------|

| 3F2              | R/W | Operations Register            |

| 3F4              | R   | Main Status Register           |

|                  | W   | Data Rate Select Register      |

| 3F5              | R/W | Data Register (FIFO)           |

| 3F7              | W   | Control Register               |

|                  | R   | Read DSKCHG (D7 only, inverse) |

# FIFO (Data)

The FIFO is used to transfer disk data. It is 16 bytes in size and has programmable threshold values. Data transfers are governed by the RQM and DIO bits in the Main Status Register.

The FIFO has the defaults with 765B compatible mode after a hardware reset. Software resets (Reset via OR or DSR register) can also place the FDC into 765B compatible mode if the LOCK bit is set to zero (See the definition of the LOCK bit in Lock command). This maintains PC-AT hardware compatibility. The default values can be changed through the Configure command (enable full FIFO operation with threshold control). The advantage of the FIFO is that it allows the system a larger DMA latency without causing a disk error. Table 4-15 gives several examples of the delays with a FIFO. The data is based upon the following formula.

Threshold#

$$X \left| \frac{1}{\text{Data Rate}} \right| X 8 - 1.5 \mu s = \text{Delay}$$

| FIFO Threshold<br>Examples | Maximum Delay to Servicing at 1 Mbps Data Rate |

|----------------------------|------------------------------------------------|

| 1 byte                     | $1 \times 8\mu s - 1.5\mu s = 6.5\mu s$        |

| 2 bytes                    | $2 \times 8 \mu s - 1.5 \mu s = 14.5 \mu s$    |

| 8 bytes                    | $8 \times 8 \mu s - 1.5 \mu s = 62.5 \mu s$    |

| 15 bytes                   | $15 \times 8\mu s - 1.5\mu s = 118.5\mu s$     |

| FIFO Threshold<br>Examples | Maximum Delay to Servicing<br>at 500 Kbps Data Rate |

|----------------------------|-----------------------------------------------------|

| 1 byte                     | $1 \times 16 \mu s - 1.5 \mu s = 14.5 \mu s$        |

| 2 bytes                    | $2 \times 16 \mu s - 1.5 \mu s = 30.5 \mu s$        |

| 8 bytes                    | $8 \times 16 \mu s - 1.5 \mu s = 126.5 \mu s$       |

| 15 bytes                   | $15 \times 16 \mu s - 1.5 \mu s = 238.5 \mu s$      |

Table 4-17. FIFO service delay

At the start of a command, the FIFO action is always disabled and command parameters must be sent based upon the RQM and DIO bit settings. As the FDC enters the command execution phase, it clears the FIFO of any data to ensure that invalid data is not transferred. An overrun or underrun will terminate the current command and the transfer of data. Disk Write will complete the current sector by generating a 00H pattern and valid CRC.

# Main Status Register (MSR)

MSR indicates the current status of the disk controller. It is always available to be read and controls the flow of data to and from the Data Register (FIFO).

Table 4-18. Main Status Register

| Bit | Symbol | Name                  | Function                                                                                                                                                                             |

|-----|--------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7  | RQM    | Request for<br>Master | Indicates that Host can access the Data Register if one. No access should be attempted if zero.                                                                                      |

| D6  | DIO    | Data In/Out           | Indicates the direction of the data transfer only when RQM is one. If one, transfer is from Data Register to Host. If zero, transfer is from Host to Data Register.                  |

| D5  | EXM    | Execution<br>Mode     | This bit is set to one only during execution phase in Non-DMA mode. When zero, execution phase has ended and result phase has started. EXM remains 0, if DMA mode is selected.       |

| D4  | СВ     | Controller<br>Busy    | A Read or Write is in progress. FDC will not accept any other command.                                                                                                               |

| D3  | F3B    | FDD 3 Busy            | If one, FDD number 3 is in seek mode. It won't accept Read or Write Command. Cleared after reading the first byte in the Result Phase of the Sense Interrupt Command for this drive. |

| D2  | F2B    | FDD 2 Busy            | Same as above for FDD 2.                                                                                                                                                             |

| D1  | F1B    | FDD 1Busy             | Same as above for FDD 1.                                                                                                                                                             |

| D0  | FOB    | FDD 0 Busy            | Same as above for FDD 0.                                                                                                                                                             |

Result Phase Status Registers (ST0, ST1, ST2, ST3)

The result phase of a command contains bytes that hold status information. The four result phase status registers are read from the Data Register only during the result phase of certain commands. Those may be read only after successfully completing a command. The particular command which has been executed determines how many of the Status Registers will be read.

Table 4-19. Status Register 0 (ST0)

| Bit | Symbol | Name             | Function                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|-----|--------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7,6 | IC     | Interrupt Code   | <ul> <li>00: Normal termination of command was completed and properly executed.</li> <li>01: Abnormal termination of command. Execution of command was started but was not successfully completed.</li> <li>10: Invalid command issue. Command which was issued was never started.</li> <li>11: Internal drive ready status changed state during the drive polling mode.</li> <li>Only occurs after a reset.</li> </ul> |  |  |  |  |  |

| 5   | SE     | Seek End         | When the FDC completes the Seek command, this flag is set to 1.                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 4   | EC     | Equipment Check  | If Track 0 signal fails to occur after 255 step pulses (Recalibrate command), then this flag is set to 1.                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 3   |        | Unused           | Always 0.                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 2   | HS     | Head Select      | Indicates the HDSEL (pin#: 80) status.                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 1,0 | DS1,0  | Drive Select 1,0 | Indicates the logical drive status selected.  00 : Drive 0, 01 : Drive 1  10 : Drive 2, 11 : Drive 3                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

Table 4-20. Status Register 1 (ST1)

| Bit | Symbol | Name            | Function                                                                                                                                     |

|-----|--------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | EN     | End of Cylinder | The FDC tried to access a sector beyond the final sector of a cylinder. It will be set if TC is not issued after Read or Write Data command. |

| 6   |        | Unused          | Always 0.                                                                                                                                    |

| 5   | DE     | Data Error      | When the FDC detects a CRC error in either ID field or data field, this flag is 1.                                                           |

| 4   | OR     | Overrun         | If the FDC is serviced by Host during data transfers within a certain timer interval, this flag is 1.                                        |

| 3   |        | Unused          | Always 0.                                                                                                                                    |

| 2   | ND     | No Data         | Any one of the following:  1. During Read (Deleted) Data command, FDC did                                                                    |

|     |        |                 | not find the specified sector.                                                                                                               |

|     |        |                 | During Read ID command, FDC cannot read the ID field without an error.                                                                       |

|     |        |                 | During Read a Track command, the FDC can not find the proper sector sequence.                                                                |

| 1   | NW     | Not Writable    | During Write (Deleted) Data or Format a Track command, if FDC detects a WP {pin#:76} signal                                                  |

| 0   | MA     | Missing Address | from the FDD, then this flag is 1.  Any one of the following:                                                                                |

|     | 17121  | Mark            | 1. The FDC did not detect an ID address mark at                                                                                              |

|     |        | Walk            | the specified track after encountering the index                                                                                             |

|     |        |                 | hole pulse twice.                                                                                                                            |

|     |        |                 | 2. The FDC can not detect a data address mark or                                                                                             |

|     |        |                 | a deleted data address mark on the specified                                                                                                 |

|     |        |                 | track.                                                                                                                                       |

Table 4-21. Status Register 2 (ST2)

| Bit       | Symbol | Name           | Function                                                                  |

|-----------|--------|----------------|---------------------------------------------------------------------------|

| 7         |        | Unused         | Always 0.                                                                 |

| 6         | СМ     | Control Mark   | Any one of the following:                                                 |

| -         |        |                | 1. During Read Data command, the FDC encoun-                              |

| <b>\$</b> |        |                | ters a deleted data address mark.                                         |

|           |        |                | During Read Deleted Data command, the FDC encounters a data address mark. |

| 5         | DE     | Data Error     | The FDC detected a CRC error in data field.                               |

| 4         | WC     | Wrong Cylinder | The track address from the sector ID field is differ-                     |

|           |        |                | ent from the track address maintained inside the                          |

|           |        |                | FDC.                                                                      |

| 3         | SE     | Scan Equal     | During Scan command, the Equal condition                                  |

|           |        | _              | satisfied.                                                                |

| 2         | SN     | Scan Not       | During Scan command, the FDC can not find a                               |

|           |        |                | sector on the cylinder which meets the desired                            |

|           |        |                | condition.                                                                |

| 1         | BC     | Bad Cylinder   | The track address from the sector ID field is differ-                     |

|           |        |                | ent from the track address maintained inside the                          |

|           |        |                | FDC and is equal to FF(hex) which indicates a bad                         |

|           |        |                | track with a hard error according to the IBM soft-                        |

|           |        |                | sectored format.                                                          |

| 0         | MD     | Missing Data   | The FDC cannot detect a data address mark or a                            |

|           |        | Address Mark   | deleted data address mark.                                                |

Table 4-22. Status Register 3 (ST3)

| Bit | Symbol | Name             | Function                              |

|-----|--------|------------------|---------------------------------------|

| 7   |        | Unused           | Always 0.                             |

| 6   | WP     | Write Protected  | Indicates the status of the WP pin.   |

| 5   |        | Unused           | Always 1.                             |

| 4   | то     | Track 0          | Indicates the status of the TRKO pin. |

| 3   | WP     | Write Protected  | Same as Bit 6                         |

| 2   | HS     | Head Select      | Same as Bit 2 of STO.                 |

| 1,0 | DS 1,0 | Drive Select 1,0 | Same as Bit 1,0 of ST0.               |

# Data Rate Select Register (DSR)

This write-only register is used to program the timings of the drive control signals. To ensure that drive timings are not violated when changing data rates, choose a drive timing such that the fastest data rate will not violate the timing. The data rate is programmed via the Control Register, not the DSR. Other applications can set the data rate in the DSR. The data rate of the floppy controller is determined by the most recent write to either the DSR or CR. The DSR is unaffected by a software reset. A hardware reset will set the DSR to 02H which corresponds to the default precompensation setting and 250 Kbps.

- D7 Software Reset: This bit behaves the same as Operations Register RESET except that this reset is self clearing.

- D6 Power Down: This bit will put the controller into the Manual Low Power mode when set to one.

- D5 Undefined. Should be set to zero.

- D4-2 Precompensation Select: These three bits select the amount of write precompensation which the floppy controller will use on the WDATA disk interface output. Table 4-21 shows the amount of precompensation used for each bit pattern. In most cases, the default values (Table 4-22) can be used; however, alternate values can be chosen for specific types of drives and media. Track 0 is the default starting track number can be changed in the Configure command.

Table 4-23. Write Precompensation Delays

| Precomp 432 | Precompensation Delay |

|-------------|-----------------------|

| 1 1 1       | 0.0ns — Disabled      |

| 0 0 1       | 41.7ns                |

| 010         | 83.3ns                |

| 0 1 1       | 125.0ns               |

| 1 0 0       | 166.7ns               |

| 1 0 1       | 208.3ns               |

| 1 1 0       | 250.0ns               |

| 000         | Default               |

Table 4-24. Default Precompensation Delays

| Data Rate | Precompensation Delay |

|-----------|-----------------------|

| 1 Mbps    | 41.7ns                |

| 500 Kbps  | 125.0ns               |

| 300 Kbps  | 125.0ns               |

| 250 Kbps  | 125.0ns               |

D1-0 Data Rate Select 1,0: These bits determine the data rate for the floppy controller. See Table 4-23 for the corresponding data rate for each value of D1, D0. The data rate select bits are unaffected by a software reset, and are set to 250 Kbps after a hardware reset.

Table 4-25. Data Rates

| Data Ra | te Select | Data Rate |          |  |

|---------|-----------|-----------|----------|--|

| 1       | 0         | MFM       | FM       |  |

| 1       | 1         | 1 Mbps    | Illegal  |  |

| l 0     | 0         | 500 Kbps  | 250 Kbps |  |

| 0       | 1         | 300 Kbps  | 150 Kbps |  |

| 1       | 0         | 250 Kbps  | 125 Kbps |  |

#### Control Register (CR)

This register sets the data rate and is write only. This is not affected by a software reset, and is set to 250 Kbps after a hardware reset. The data rate of the floppy controller is determined by the last write to either this register or DSR.

D7-2 Reserved: Should be set to 0.

D1-0 Data Rate Select 1,0: See Table 4-23 for the appropriate values.

# Operations Register (OR)

This register controls the drive select and motor, enable disk interface outputs, enables the DMA logic, and contains a software reset bit. It is set to 00H after a hardware reset, and is unaffected by a software reset.

2 Drive Select (Bit 7 of FSR is 0)

D7-6 Should be 0.

D5 Motor on enable: Inverted output MTR1 (pin#: 71) is active D4 Motor on enable: Inverted output MTR0 (pin#: 68) is active

D3 DMA enable : Set to 1 will enable the DRQ, DACK, TC and IRQ6 pins.

Set to 0 will disable TC, DACK pins and make IRQ6, DRQ pins Hi-Z state.

D2 Software Reset : Active low software reset signal.

D1 Should be 0

D0 Drive Select: If 0 and D4 = 1, then DS0 (pin#: 70) is active.

If 1 and D5=1, then DS1 (pin#: 69) is active.

4 Drive Select (Bit 7 of FSR is 1)

Table 4-26, Operations Register for 4 Drive support

|   | Bits |   |   |   |   | Drive Pins |     |      |      |                        |

|---|------|---|---|---|---|------------|-----|------|------|------------------------|

| 7 | 6    | 5 | 4 | 1 | 0 | DS1        | DS0 | MTR1 | MTR0 | Encoded Functions      |

|   |      |   | 1 | 0 | 0 | 0          | 0   | 0    | 0    | Active Drive & Motor 0 |

| 1 |      | 1 |   | 0 | 1 | 0          | 1   | 0    | 1    | Active Drive & Motor 1 |

| ļ | 1    |   |   | 1 | 0 | 1          | 0   | 1    | 0    | Active Drive & Motor 2 |

| 1 |      |   |   | 1 | 1 | 1          | 1   | 1    | 1    | Active Drive & Motor 3 |

<sup>\*:</sup> Bits 2 and 3 are the same as 2 Drive select.

During command or result phase, the main status register must be read by the processor before each byte of information is written into or read from the data register. Bit 6 and 7 in the main status register must be in a 0 and 1 state, respectively, before each byte of the command word may be written into the FDC. Many of the commands require multiple bytes, and as a result the main status register must be read prior to each byte transfer to the FDC. On the other hand, during the result phase, bit 6 and 7 in the main status register must both be 1's before reading each byte from the data register. (This reading of the main status register before each byte transfer to the FDC is required in only the command and result phases, and not during the execution phase.)

During the execution phase, the main status register need not be read. If the FDC is in the Non-DMA mode, then the receipt of each data byte (if FDC is reading data from FDD) is indicated by an interrupt signal on IRQ6 pin. The generation of a read signal will reset the interrupt as well as output the data onto the data bus. For example, if the processor cannot handle interrupt fast enough then it may poll the main status register and then bit 7 (RQM) functions just like the interrupt signal. If a Write command is in process, then the write signal performs the reset to the interrupt signal.

It is important to note that during the result phase all bytes shown in the command table must be read. The Read Data Command, for example has seven bytes of data in the result phase. All seven bytes must be read in order to successfully complete the Read Data Command. The FDC will not accept a new command until all seven bytes have been read. Other commands may require fewer bytes to be read during the result phase.

The bytes of data which are sent to the FDC to form the command phase, and are read out of the FDC in the result phase, must occur in the order shown in the command table. That is, the command code must be sent first and the other bytes sent in the prescribed sequence. No. foreshortening of the command or result phases are allowed. After the last byte of data in the command phase is sent to the FDC, the execution phase automatically starts. In a similar fashion, when the last byte of data is read out in the result phase, the command is automatically ended and the FDC is ready for a new command. A command may be aborted by simply sending a Terminal Count signal to TC pin. This is a convenient means of ensuring that the processor may always get the FDC's attention even if the disk system hangs up in an abnormal manner.

The FDC continues to transfer data until the TC input is active. In Non-DMA Host transfers are not the normal precedure. If the user chooses to do so, the FDC will successfully complete commands, but will always give abnormal termination error status since TC is qualified by an inactive NACK. In Non-DMA mode it is necessary to examine the main status register to determine the cause of the interrupt since it could be a data interrupt or a command termination interrupt, either normal or abnormal.

If the FDC is in the DMA mode, no interrupts are generated during the execution phase. The FDC generates DRQ's (DMA Requests) when each byte of data is available. The DMA controller responds to this request with both a DACK = 0 (DMA Acknowledge) and a RD = 0 (host read). If a Write Command has been programmed then a Host write signal will appear instead of Host read. After the execution phase has been completed (TC occurred), then an interrupt will occur (IRQ6 = 1). This signifies the beginning of the result phase. When the first byte of data is read during the result phase, the interrupt is automatically reset (IRQ6 = 0).

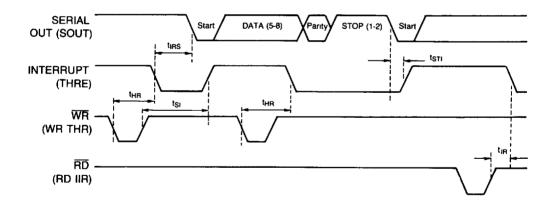

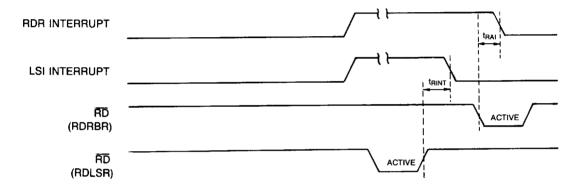

# 4.3 Serial Ports

Serial ports are completely independent. They perform serial-to-parallel conversion or parallel-to-serial conversion between a peripheral device or a MODEM and CPU.

Serial Ports Registers

Internal registers are classified by three types, that is data, status, and control registers. The data registers are the Receiver Buffer Register and the Transmitter Holding Register. The status registers are the Line Status Register and the Modern Status Register. Also the control registers are Divisor Latch LSB and Divisor Latch MSB for baudrate selection.

Line Control Register

This register decides the format of the asynchronous serial data. Figure 1. shows 1 byte serial data composition and details on each bit are described on Figure 2.

Table 4-27. Register Address NIOL = 0, AEN = 0

| DLAB1 | UART-CS1 | A2 | A1 | A0         | Register                        |             |

|-------|----------|----|----|------------|---------------------------------|-------------|

| 0     | 1        | 0  | 0  | 0          | Receiver Buffer (Read)          |             |

|       |          |    |    |            | Transmitter Holding (Write) A   |             |

| 0     | 1        | 0  | 0  | 1          | Interrupt Enable                | R           |

| 0     | 1        | 0  | 1  | 0          | Interrupt Identification (Read) | Т           |

| 0     | 1        | 0  | 1  | 0          | Test Control (Write)            |             |

| X     | 1        | 0  | 1  | 1          | Line Control                    | ļ           |

| X     | 1        | 1  | 0  | 0          | MODEM Control                   | 1           |

| X     | 1        | 1  | 0  | 1          | Line Status                     |             |

| X     | 1        | 1  | 1  | 0          | MODEM Status                    |             |

| X     | 1        | 1  | 1  | 1          | Scratch (Note 1)                | 1           |

| 1     | 1        | 0  | 0  | 0          | Divisor Latch                   |             |

|       |          |    |    |            | (Least Significant Byte)        |             |

| 1     | l I      | 0  | 0  | 1          | Divisor Latch                   |             |

|       |          |    |    |            | (Most Significant Byte)         |             |

| DLAB2 | UART-CS1 | A2 | A1 | <b>A</b> 0 | Register                        | <del></del> |

| 0     | 0        | 0  | 0  | 0          | Receiver Buffer (Read) U        |             |

|       |          |    |    |            | Transmitter Holding (Write)     | A           |

| 0     | 0        | 0  | 0  | 1          | Interrupt Enable                | R           |

| 0     | 0        | 0  | 1  | 0          | Interrupt Identification (Read) | T           |

| 0     | 0        | 0  | 1  | 0          | Test Control (Write)            |             |

| X     | 0        | 0  | 1  | 1          | Line Control                    |             |

| X     | 0        | 1  | 0  | 0          | MODEM Control                   | 2           |

| X     | 0        | 1  | 0  | 1          | Line Status                     |             |

| X     | 0        | 1  | 1  | 0          | MODEM Status                    |             |

| X     | 0        | 1  | 1  | 1          | Scratch (Note 1)                |             |

| 1     | 0        | 0  | 0  | 0          | Divisor Latch                   |             |

|       |          |    |    |            | (Least Significant Byte)        |             |

| 1     | 0        | 0  | 0  | 1          | Divisor Latch                   |             |

|       |          |    |    |            | (Most Significant Byte)         |             |

Note 1: This register is only present when operating in the AT mode.

Table 4-28. Summary of Registers

|           | Register Address                                |                                                       |                                                                               |                                                  |                                                 |                                             |                                    |                                              |                                             |                     |                          |                          |

|-----------|-------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------------------|---------------------------------------------|------------------------------------|----------------------------------------------|---------------------------------------------|---------------------|--------------------------|--------------------------|

|           | 0 DLAB=0                                        | 0 DLAB = 0                                            | 1 DLAB=0                                                                      | 1                                                | 2                                               | 3                                           | 4                                  | 5                                            | 6                                           | 7                   | 0 DLAB=1                 | 1 DLAB=1                 |

| Bit<br>No | Receiver<br>Buffer<br>Register<br>(Read<br>Only | Transmitter<br>Holding<br>Register<br>(Write<br>Only) | Interrupt<br>Enable<br>Register                                               | Interrupt<br>Ident<br>Register<br>(Read<br>Only) | FIFO<br>Control<br>Register<br>(Write)<br>Only) | Line<br>Control<br>Register                 | MODEM<br>Control<br>Register       | Line<br>Status<br>Register                   | MODEM<br>Status<br>Register                 | Scratch<br>Register | Divisor<br>Latch<br>(LS) | Divisor<br>Latch<br>(MS) |

|           | RBR                                             | THR                                                   | IER                                                                           | IIR                                              | FCR                                             | LCR                                         | MCR                                | LSR                                          | MSR                                         | SCR                 | DLL                      | DLM                      |

| 0         | Data Bit 0<br>(Note 1)                          | Data Bit 0                                            | Enable<br>Received<br>Data<br>Available<br>Interrupt<br>(ERBFI)               | "0" if<br>Interrupt<br>Pending                   | FIFO<br>Enable                                  | Word<br>Length<br>Select<br>Bit 0<br>(WLS0) | Data<br>Terminal<br>Ready<br>(DTR) | Data<br>Ready<br>(DR)                        | Delta<br>Clear<br>to Send<br>(DCTS)         | Bit 0               | Bit 0                    | Bit 8                    |

| 1         | Data Bit 1                                      | Data Bit 1                                            | Enable<br>Transmitter<br>Holding<br>Register<br>Empty<br>Interrupt<br>(ETBEI) | Interrupt<br>ID<br>Bit (0)                       | RCVR<br>FIFO<br>Reset                           | Word<br>Length<br>Select<br>Bit 1<br>(WLS1) | Request<br>to Send<br>(RTS)        | Overrun<br>Error<br>(OE)                     | Delta<br>Data<br>Set<br>Ready<br>(DDSR)     | Bit 1               | Bit 1                    | Bit 9                    |

| 2         | Data Bit 2                                      | Data Bit 2                                            | Enable<br>Receiver<br>Line Status<br>Interrupt<br>[ELSI]                      | Interrupt<br>ID<br>Bit (1)                       | XMIT<br>FIFO<br>Reset                           | Number of<br>Stop Bits<br>(STB)             | Out 1                              | Parity<br>Error<br>(PE)                      | Trading<br>Edge Ring<br>Indicator<br>(TERI) | Bit 2               | Bit 2                    | Bit 10                   |

| 3         | Data Bit 3                                      | Data Bit 3                                            | Enable<br>MODEM<br>Status<br>Interrupt<br>(EDSSI)                             | Interrupt<br>ID<br>Bit (2)<br>(Note 2)           | DMA<br>Mode<br>Select                           | Parity<br>Enable<br>(PEN)                   | Out 2                              | Framing<br>Error<br>(FE)                     | Delta Data Camer Delect (DDCD)              | Bit 3               | Bit 3                    | Bit 11                   |

| 4         | Data Bit 4                                      | Data Bit 4                                            | 0                                                                             | 0                                                | Reserved                                        | Even<br>Parity<br>Select<br>(EPS)           | Loop                               | Break<br>Interrupt<br>(BI)                   | Clear<br>to<br>Send<br>(CTS)                | Bit 4               | Bit 4                    | Bit 12                   |

| 5         | Data Bit 5                                      | Data Bit 5                                            | 0                                                                             | 0                                                | Reserved                                        | Stick<br>Parity                             | 0                                  | Transmitter<br>Holding<br>Register<br>(THRE) | Data<br>Set<br>Ready<br>(DSR)               | Bit 5               | Bit 5                    | Bit 13                   |

| 6         | Data Bit 6                                      | Data Bit 6                                            | 0                                                                             | FIFO3<br>Enableed<br>(Note 2)                    | RCVR<br>Trigger<br>(LSB)                        | Set<br>Break                                | 0                                  | Transmitter<br>Empty<br>(TEMT)               | Ring<br>Indicator<br>(RI)                   | Bit 6               | Bit 6                    | Bit 14                   |

| 7         | Data Bit 7                                      | Data Bit 7                                            | 0                                                                             | FIFO3<br>Enabled<br>(Note 2)                     | RCVR<br>Trigger<br>(MSB)                        | Divisor<br>Latch<br>Access Bit<br>(DLA3)    | 0                                  | Error in<br>RCVR<br>FIFO<br>(Note 2)         | Data<br>Carrier<br>Detect<br>(DCD)          | Bit 7               | Bit 7                    | Bit 15                   |

Note 1.: Bit 0 is the least significant bit seriously transmitted or received. 2.: These bits are always 0 in the GM16C450 Mode.

#### Registers

The system programmer may be access any of the UART registers summarized in Table II via the CPU. These registers control UART operations including transmission and reception of data. Each register bit in Table II has its name and reset states shown

#### LINE CONTROL REGISTER

The system programmer specifies the format of the asynchronous data communications exchange and set the Divisor Latch Access bit via the Line Control Register (LCR). The programmer can also read the contents of the Line Control Register. The read capability simplifies system programming and eliminates the need for separate storage in system memory of the line characteristics. Table II shows the contents of the LCR. Details on each bit follow:

Bit 0 and 1: These two bits specify the number of bits in each transmitted or received serial character. The encoding of bits 0 and 1 is as follows

| Bit 1 | Bit 0 | Character Length |

|-------|-------|------------------|

| 0     | 0     | 5 Bits           |

| 0     | 1     | 6 Bits           |

| 1     | 0     | 7 Bits           |

| 1     | 1     | 8 Bits           |

- Bit 2: This bit specifies the number of Stop bits transmitted and received in each serial character. If bit 2 is a logic 0, one Stop bit is generated in the transmitted data. If Bit 2 is a logic 1 when a 5-bit word length is selected via bits 0 and 1, one and a half Stop bits are generated. If bit 2 is a logic 1 when either a 6-, 7-, or 8-bit word length is selected, two Stop bit are generated. The Receiver checks the first Stop bit only, regardless of the number of Stop bit selected.

- Bit 3: This bit is the Parity Enable bit. When bit 3 is a logic 1, a parity bit is generated (transmit data) or checked (receive data) between the last data word bit and Stop bit of the serial data. (The Parity bit is used to produce an even or odd number of 1s when the data word bits and the Parity bit are summed).

- Bit 4: This bit is the Even Parity Select bit. When bit 3 is a logic 1 and bit 4 is a logic 0, and odd number of logic 1s is transmitted or checked in the data word bits and parity bit. When bit 3 is a logic 1 and bit 4 is a logic 1, an even number of logic 1s is transmitted or checked.

- Bit 5: This bit is the Stick Parity bit. When bit 3, 4 and 5 are logic 1 the Parity bit is transmitted and checked as a logic 0. If bit 3 and 5 are 1 and bit 4 is a logic 0 then the Parity bit is transmitted and checked as a logic 1. If bit 5 is a logic 0 Stick Parity is disabled.

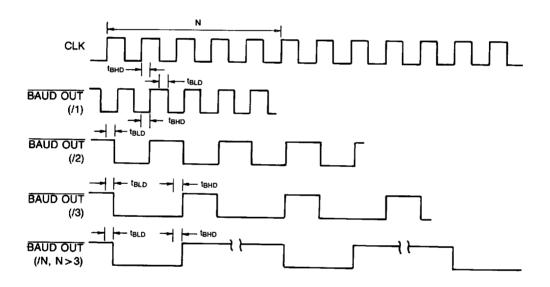

- Bit 6: This bit is the Break Control bit. It causes a break condition to be transmitted to the received UART. When it is set to logic 1, the serial output (SOUT) is forced to the Spacing (logic 0) state. The break is disabled by setting bit 6 to a logic 0. The Break Control bit acts only on SOUT and has no effect on the transmitted logic.